# Improving Processor Performance and Simulation Methodology

A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA BY

Joshua Jeffrey Yi

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

David J. Lilja, Advisor

December 2003

## **UNIVERSITY OF MINNESOTA**

This is to certify that I have examined this copy of a doctoral dissertation by

Joshua Jeffrey Yi

and have found that it is complete and satisfactory in all respects, and that any and all revisions required by the final examining committee have been made.

| Name of Faculty Adviser(s)      |  |

|---------------------------------|--|

|                                 |  |

| Signature of Faculty Adviser(s) |  |

|                                 |  |

|                                 |  |

**GRADUATE SCHOOL**

**Date**

# Acknowledgements

As the end of my days as a graduate student draws nigh, I have the occasion to reflect upon the many long days, and the even longer nights, that all too quickly lengthened into years, that finally culminated with a doctorate in Electrical Engineering, *dei gratia*. What this reflection – tinged with nostalgia – has revealed is that the splendor of this achievement is possible only as a result of the support of others. And while my name shall be the only one on the diploma, these others deserve similar or equal recognition. Accordingly, I would like to avail myself of this opportunity to gratefully thank those people who unfailingly supported and comforted me when I was disheartened, gently challenged and questioned me when it was necessary, and, finally, loved me always. To you, I owe a debt that my clumsy eloquence cannot fully articulate and that my feeble efforts can never adequately remunerate.

I would first wish to acknowledge the infinite debt that I owe to my God and His Son, the Lord Jesus Christ, the sovereign Lord of my life. I also wish to thank God and Christ Jesus for His tender compassion and mercy, His everlasting love and goodness, His unmerited favor and blessings, and His perfect peace and golden happiness. Without any and all of these gifts, this dissertation would have been impossible.

Praise the Lord, O my soul, and forget not all His benefits – who forgives all your sins and heals all your diseases, who redeems your life from the pit and crowns you with love and compassion, who satisfies your desires with good things so that your youth is renewed like the eagle's.

- Psalm 103:2-5

I also am profoundly indebted to my advisor, Professor David Lilja, for his technical knowledge, his generous financial assistance through many of my years of graduate school, his unflagging encouragement, and especially his ample patience (as he had to

listen to my complaints, answer my many questions, and endure my stubbornness). He also had faith in my abilities when others, often including myself, had doubts. Above these characteristics, however, the fundamental principles that I learned from him were professional integrity and gentlemanly deportment. My one professional aspiration is to, one day, be as fondly regarded by my students as he is by me, and to engender the same deep respect from my colleagues.

I would also like to recognize the invaluable help that was freely and generously given to me by Professor Douglas Hawkins, Professor Wei-Chung Hsu, and Professor Pen-Chung Yew. I would like to thank Professor Hawkins for all the statistical help that he gave to this statistical neophyte in the form of lengthy e-mail replies and through clear explanations of statistical principles. Professor Hsu, over the years, challenged me with pointed questions to achieve more than I already had and to further improve the quality and depth of my work. For these things, I am grateful. Finally, I would like to thank Professor Yew for his encouragement and counsel.

I would also like to thank Professor Sachin Sapatnekar and Professor George Karypis, two of my doctoral examination committee members, for their willingness to serve on my committee and for their insightful comments and criticisms.

I would like to acknowledge the technical advice, the all-too-often unrequited help, and, foremost, the friendship that was given to me by Ying Chen, Youngsoo Choi, Peng-fei Chuang, Bob Glamm, Chris Hescott, Baris Kazar, Sreekumar Kodakara, Dr. Jin Lin, Keith Osowski, Professor Resit Sendag, and Keqiang Wu. We laughed together, we "enjoyed life" together, and we grew up as engineers – and as people – together. Collectively, you inspired me, you challenged me, and you reassured me. Truly, our shared memories make parting such sweet sorrow.

And finally, to my family, I offer my most heartfelt and gracious thanks. To my parents, C. James Yi, Ph.D. and Judy Yi, and to my sisters, Jennifer Yi, Ph.D. and Joanna Yi, M.D.-to-be, the work encapsulated in this dissertation was possible only with your

steadfast encouragement, your earnest prayers, and your loving comfort. You lifted me up when I was down, you brightened my path in the midst of stormy trials, and you sustained my confidence in times of doubt. For these things, and the countless others that are not written here, since any words that I may muster are starkly pale in comparison, I simply say, thank you, and thank you for loving me.

Joshua J. Yi

December 2003

Minneapolis, Minnesota

Soli Deo Gloria

# **Table of Contents**

| A | bstract  |                                                            | XII |

|---|----------|------------------------------------------------------------|-----|

| 1 | Introdu  | ction                                                      | 1   |

|   | 1.1      | Superscalar Microprocessors                                | 2   |

|   | 1.2      | Instruction-Level Parallelism and Data Dependences         | 4   |

|   | 1.3      | Superscalar Performance                                    | 6   |

|   | 1.4      | Redundant Computations                                     | 7   |

|   | 1.5      | Value Reuse: Effect and Shortcomings                       | 9   |

|   | 1.6      | Instruction Precomputation                                 | 10  |

|   | 1.7      | Simplification and Elimination of Trivial Computations     | 11  |

|   | 1.8      | The Efficacy, Utility, and Necessity of Simulators         | 13  |

|   | 1.9      | The Deficiencies of Existing Simulation Methodologies      | 14  |

|   | 1.10     | Contributions of this Dissertation                         | 17  |

|   | 1.11     | Dissertation Organization                                  | 17  |

| 2 | Instruct | tion Precomputation                                        | 19  |

|   | 2.1      | Problems with Existing Value Reuse Mechanisms              | 19  |

|   | 2.2      | The Amount of Redundant Computation                        | 21  |

|   |          | 2.2.1 Global-Level Redundant Computations                  | 23  |

|   |          | 2.2.2 A Comparison of the Amount of Global and Local Level |     |

|   |          | Redundant Computation                                      | 26  |

|   | 2.3      | The Mechanics of Instruction Precomputation                | 29  |

|   |          | 2.3.1 How it Improves Performance                          | 33  |

|   | 2.4      | A Comparison of Instruction Precomputation and Value Reuse | 34  |

| 3 | Trivial  | Computations                                               | 35  |

|   | 3.1      | Definition of Trivial Computations and How to Exploit Them | 35  |

|   | 3.2      | The Amount of Trivial Computations                         | 37  |

|   | 3.3     | The Mechanics of Trivial Computation Simplification and Eliminatio | n 41 |

|---|---------|--------------------------------------------------------------------|------|

|   | 3.4     | Hardware Cost to Simplify and Eliminate Trivial Computations       | 44   |

| 4 | Simulat | ion Methodology                                                    | 45   |

|   | 4.1     | An Overview of Simulation Methodology                              | 45   |

|   |         | 4.1.1 Principal Steps of the Simulation Process                    | 47   |

|   |         | 4.1.2 Focus of this Dissertation                                   | 50   |

|   | 4.2     | Fractional Multifactorial Design of Experiments                    | 51   |

|   |         | 4.2.1 Comparison of Statistical Designs                            | 52   |

|   |         | 4.2.1.1 One-at-a-Time Design                                       | 52   |

|   |         | 4.2.1.2 Full Multifactorial Design: Analysis of Variance           |      |

|   |         | (ANOVA) Design                                                     | 53   |

|   |         | 4.2.1.3 Fractional Multifactorial Design: Plackett and Burman      | l    |

|   |         | Design                                                             | 55   |

|   |         | 4.2.2 Mechanics of Plackett and Burman Designs                     | 56   |

|   | 4.3     | Processor Parameter Selection                                      | 59   |

|   | 4.4     | Benchmark Selection                                                | 61   |

|   | 4.5     | Analysis of a Processor Enhancement                                | 62   |

|   | 4.6     | Summary                                                            | 64   |

| 5 | Experir | nental Framework                                                   | 66   |

|   | 5.1     | The SimpleScalar Superscalar Simulator                             | 66   |

|   | 5.2     | Instruction Precomputation and Trivial Computation Parameters      | 67   |

|   | 5.3     | Plackett and Burman Parameters                                     | 69   |

|   | 5.4     | Benchmarks and Input Sets                                          | 72   |

| 6 | Perform | nance Evaluation                                                   | 76   |

|   | 6.1     | Instruction Precomputation Performance Results                     | 76   |

|   |         | 6.1.1 Upper-Bound – Profile A, Run A                               | 77   |

|   |         | 6.1.2 Different Input Sets – Profile B, Run A                      | 80   |

|   |         | 6.1.3 Combination of Input Sets – Profile AB, Run A                | 82   |

|   |         | 6.1.4                                                          | Frequency versus Frequency and Latency Product                                                                                                                                                                                                                  | 85                                            |

|---|---------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   |         | 6.1.5                                                          | Performance of Instruction Precomputation versus Value Reuse                                                                                                                                                                                                    | 87                                            |

|   |         | 6.1.6                                                          | Summary                                                                                                                                                                                                                                                         | 89                                            |

|   | 6.2     | Perfor                                                         | mance Results for Exploiting Trivial Computations                                                                                                                                                                                                               | 89                                            |

|   |         | 6.2.1                                                          | Realistic Processor Configuration                                                                                                                                                                                                                               | 90                                            |

|   |         | 6.2.2                                                          | Enhanced Processor Configuration                                                                                                                                                                                                                                | 92                                            |

|   |         | 6.2.3                                                          | Summary                                                                                                                                                                                                                                                         | 95                                            |

|   | 6.3     | The R                                                          | esults of Applying a Statistically Rigorous Simulation                                                                                                                                                                                                          |                                               |

|   |         | Metho                                                          | odology                                                                                                                                                                                                                                                         | 95                                            |

|   |         | 6.3.1                                                          | Analysis of Processor Parameters for Parameter Value                                                                                                                                                                                                            |                                               |

|   |         |                                                                | Selection                                                                                                                                                                                                                                                       | 96                                            |

|   |         | 6.3.2                                                          | Analysis of Benchmarks for Benchmark Selection                                                                                                                                                                                                                  | 101                                           |

|   |         | 6.3.3                                                          | Analysis of the Effect of Processor Enhancements                                                                                                                                                                                                                | 104                                           |

|   |         | 6.3.4                                                          | Summary                                                                                                                                                                                                                                                         | 108                                           |

| 7 | Related | Work                                                           |                                                                                                                                                                                                                                                                 | 109                                           |

|   | 7.1     | Volue                                                          | Locality                                                                                                                                                                                                                                                        | 109                                           |

|   | /.1     | v alue                                                         |                                                                                                                                                                                                                                                                 |                                               |

|   | 7.1     | 7.1.1                                                          | Redundant Computations                                                                                                                                                                                                                                          | 110                                           |

|   | 7.1     | 7.1.1                                                          | •                                                                                                                                                                                                                                                               | 110<br>111                                    |

|   |         | 7.1.1<br>Value                                                 | Reuse and Prediction                                                                                                                                                                                                                                            |                                               |

|   |         | 7.1.1<br>Value                                                 | Reuse and Prediction Value Reuse                                                                                                                                                                                                                                | 111<br>111                                    |

|   |         | 7.1.1<br>Value<br>7.2.1                                        | Reuse and Prediction  Value Reuse  Value Prediction                                                                                                                                                                                                             | 111                                           |

|   |         | 7.1.1<br>Value<br>7.2.1                                        | Reuse and Prediction  Value Reuse  Value Prediction  7.2.2.1 Simple Value Predictors                                                                                                                                                                            | 111<br>111<br>114<br>115                      |

|   |         | 7.1.1<br>Value<br>7.2.1<br>7.2.2                               | Reuse and Prediction  Value Reuse  Value Prediction  7.2.2.1 Simple Value Predictors  7.2.2.2 Complex (Hybrid) Value Predictors                                                                                                                                 | 111<br>111<br>114                             |

|   | 7.2     | 7.1.1<br>Value<br>7.2.1<br>7.2.2<br>Simpli                     | Reuse and Prediction  Value Reuse  Value Prediction  7.2.2.1 Simple Value Predictors  7.2.2.2 Complex (Hybrid) Value Predictors  ification and Elimination of Trivial Computations                                                                              | 111<br>111<br>114<br>115<br>116               |

|   | 7.2     | 7.1.1<br>Value<br>7.2.1<br>7.2.2<br>Simpli                     | Reuse and Prediction  Value Reuse  Value Prediction  7.2.2.1 Simple Value Predictors  7.2.2.2 Complex (Hybrid) Value Predictors  ification and Elimination of Trivial Computations  Work in Simulation Methodology                                              | 111<br>114<br>115<br>116<br>117               |

|   | 7.2     | 7.1.1<br>Value<br>7.2.1<br>7.2.2<br>Simpli                     | Reuse and Prediction  Value Reuse  Value Prediction  7.2.2.1 Simple Value Predictors  7.2.2.2 Complex (Hybrid) Value Predictors  ification and Elimination of Trivial Computations  Work in Simulation Methodology  Simulation Validation                       | 111<br>111<br>114<br>115<br>116<br>117        |

|   | 7.2     | 7.1.1<br>Value<br>7.2.1<br>7.2.2<br>Simpli<br>Prior V<br>7.4.1 | Reuse and Prediction Value Reuse Value Prediction 7.2.2.1 Simple Value Predictors 7.2.2.2 Complex (Hybrid) Value Predictors ification and Elimination of Trivial Computations Work in Simulation Methodology Simulation Validation Reducing the Simulation Time | 111<br>111<br>114<br>115<br>116<br>117<br>119 |

| 8                                 | Future   | Work                                                   | 128 |

|-----------------------------------|----------|--------------------------------------------------------|-----|

|                                   | 8.1      | Instruction Precomputation                             | 128 |

|                                   | 8.2      | Simplification and Elimination of Trivial Computations | 129 |

|                                   | 8.3      | Improving Computer Architecture Simulation and Design  |     |

|                                   |          | Methodology                                            | 130 |

|                                   |          | 8.3.1 Simulation Methodology                           | 130 |

|                                   |          | 8.3.2 Design Methodology                               | 133 |

| 9                                 | Conclu   | sion                                                   | 134 |

| Bi                                | bliograp | ohy                                                    | 140 |

| Appendix A – Supplemental Results |          | 144                                                    |     |

| $\mathbf{A}$                      | ppendix  | B – List of Publications                               | 165 |

# **List of Figures**

| Figure 1.1.1          | Functional-Level Organization of a Superscalar Processor | 3  |

|-----------------------|----------------------------------------------------------|----|

| Figure 1.2.1          | Assembly Code Example of Read-After-Write Dependences    | 4  |

| Figure 1.4.1          | Example of a Source of Redundant Computations            | 7  |

| Figure 1.4.2          | Example of Global and Local Level Redundant              |    |

|                       | Computations                                             | 8  |

| Figure 2.1.1          | Four-Entry Value Reuse Table and its Processor Interface | 20 |

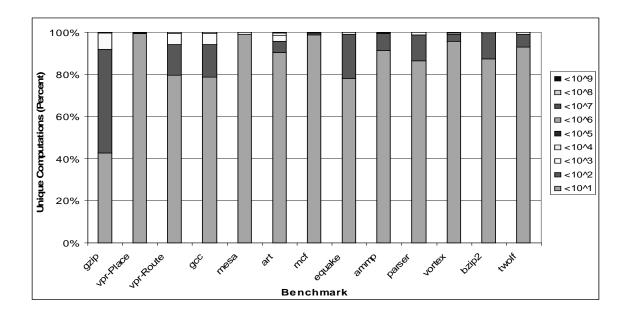

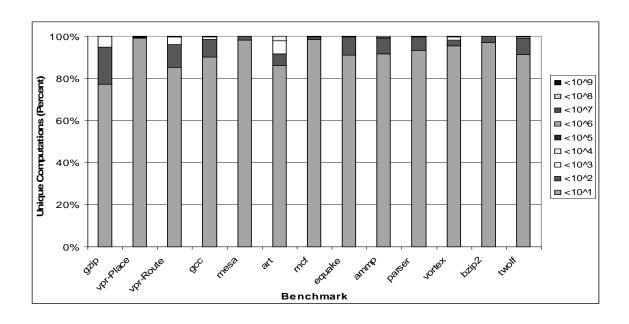

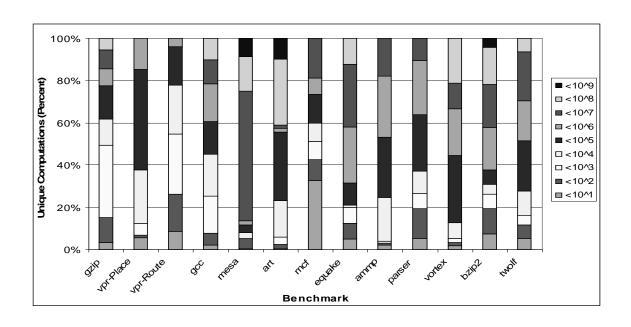

| <b>Figure 2.2.1.1</b> | Frequency Distribution of Unique Computations per        |    |

|                       | Benchmark, Global-Level, Normalized                      | 23 |

| <b>Figure 2.2.1.2</b> | Percentage of Dynamic Instructions Due to the Unique     |    |

|                       | Computations in each Frequency Range, Global-Level,      |    |

|                       | Normalized                                               | 24 |

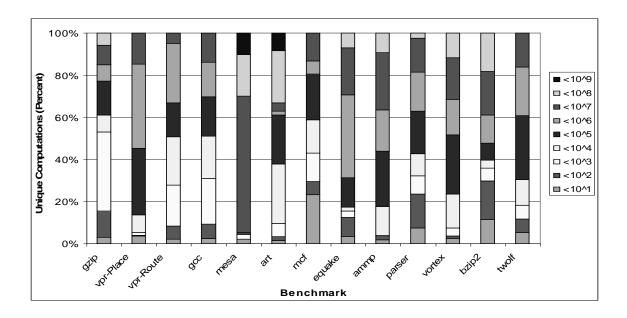

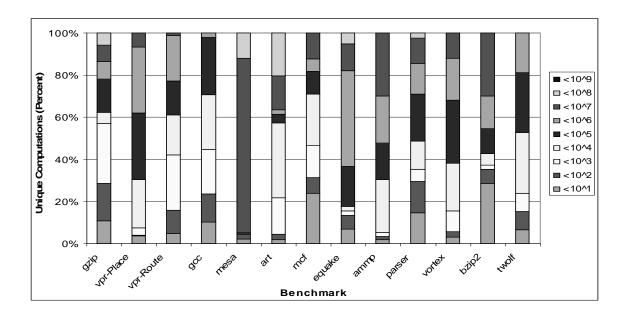

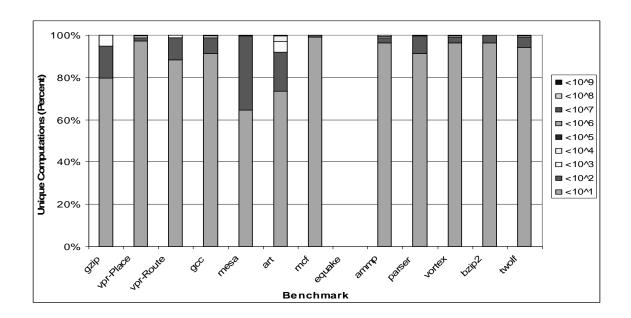

| <b>Figure 2.2.2.1</b> | Frequency Distribution of Unique Computations per        |    |

|                       | Benchmark, Local-Level, Normalized                       | 27 |

| <b>Figure 2.2.2.2</b> | Percentage of Dynamic Instructions Due to the Unique     |    |

|                       | Computations in each Frequency Range, Local-Level,       |    |

|                       | Normalized                                               | 27 |

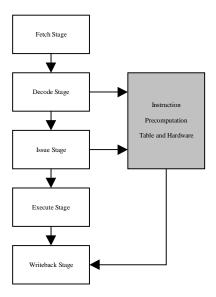

| <b>Figure 2.3.1</b>   | Operation of a Superscalar Pipeline with Instruction     |    |

|                       | Precomputation                                           | 32 |

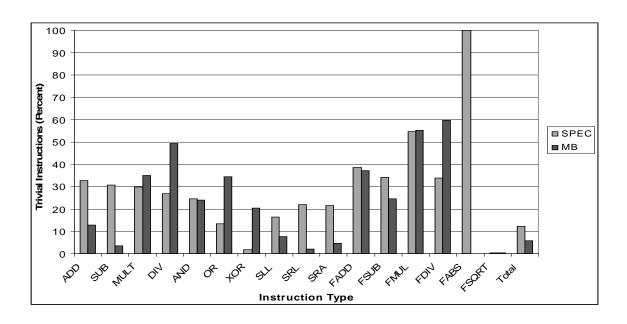

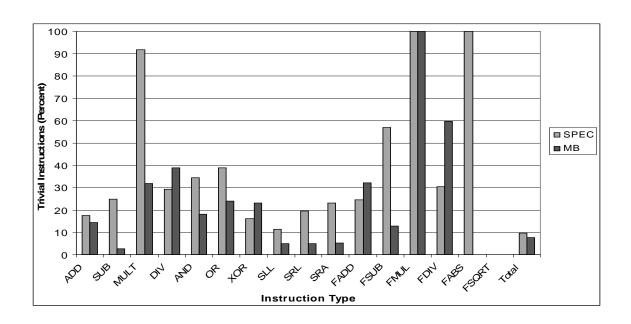

| <b>Figure 3.2.1</b>   | Percentage of Trivial Computations per Instruction Type  |    |

|                       | and per Total Number of Dynamic Instructions for the     |    |

|                       | SPEC and MediaBench Benchmarks                           | 40 |

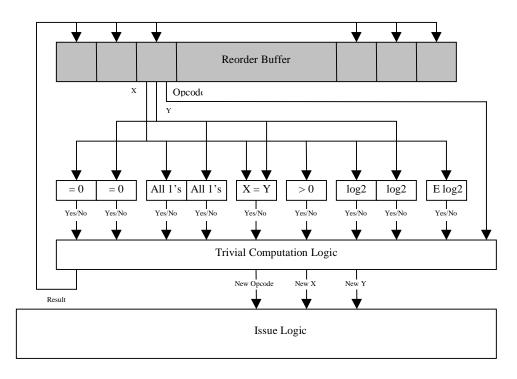

| <b>Figure 3.3.1</b>   | Trivial Computation Hardware and Its Processor Interface | 42 |

| Figure 6.1.1.1        | Speedup Due to Instruction Precomputation; Profile Input |    |

|                       | Set A, Run Input Set A, Frequency                        | 78 |

| Figure 6.1.2.1        | Speedup Due to Instruction Precomputation; Profile Input |    |

|                       | Set B, Run Input Set A, Frequency                        | 80 |

| <b>Figure 6.1.3.1</b>  | Speedup Due to Instruction Precomputation; Profile Input  |     |

|------------------------|-----------------------------------------------------------|-----|

|                        | Set AB, Run Input Set A, Frequency                        | 83  |

| <b>Figure 6.1.4.1</b>  | Speedup Due to Instruction Precomputation for the Highest |     |

|                        | Frequency and Latency Product Unique Computations;        |     |

|                        | Profile B, Run A                                          | 86  |

| <b>Figure 6.1.5.1</b>  | Speedup Due to Value Reuse; Run A                         | 88  |

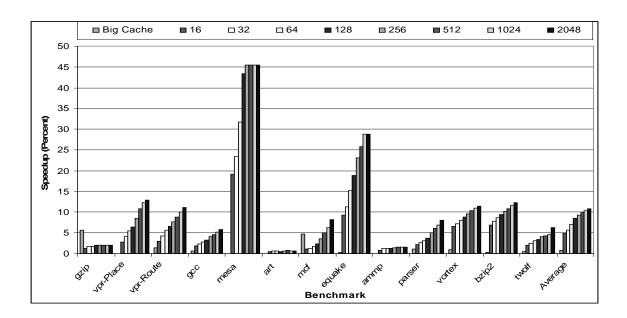

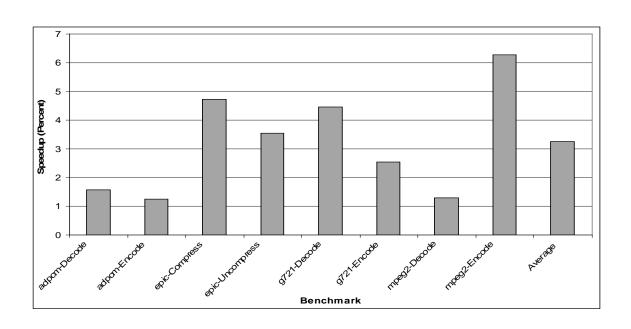

| <b>Figure 6.2.1.1</b>  | Speedup Due to the Simplification and Elimination of      |     |

|                        | Trivial Computations for Selected SPEC 2000               |     |

|                        | Benchmarks, Realistic Processor Configuration             | 90  |

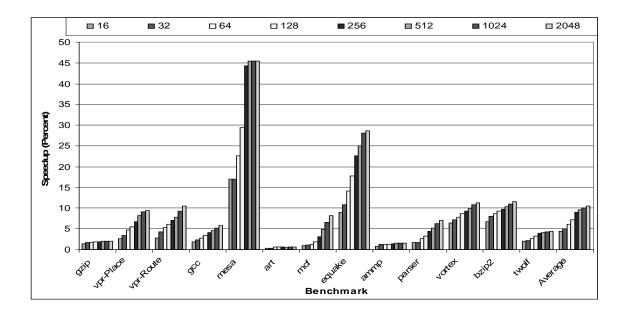

| <b>Figure 6.2.1.2</b>  | Speedup Due to the Simplification and Elimination of      |     |

|                        | Trivial Computations for Selected MediaBench              |     |

|                        | Benchmarks, Realistic Processor Configuration             | 91  |

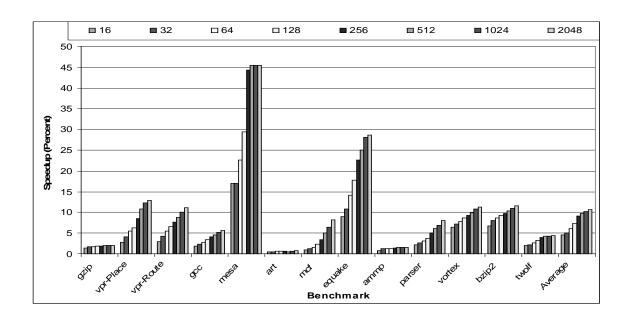

| <b>Figure 6.2.2.1</b>  | Speedup Due to the Simplification and Elimination of      |     |

|                        | Trivial Computations for Selected SPEC 2000               |     |

|                        | Benchmarks, Enhanced Processor Configuration              | 93  |

| <b>Figure 6.2.2.2</b>  | Speedup Due to the Simplification and Elimination of      |     |

|                        | Trivial Computations for Selected MediaBench              |     |

|                        | Benchmarks, Enhanced Processor Configuration              | 94  |

| <b>Figure 6.3.2.1</b>  | Cluster Analysis Results (i.e. Dendrogram) for the Large  |     |

|                        | MinneSPEC Input Set                                       | 102 |

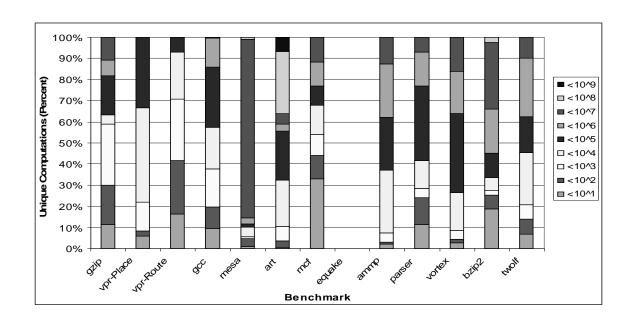

| Figure A2.2.1.1        | Frequency Distribution of Unique Computations per         |     |

|                        | Benchmark, Global-Level, Normalized, Input Set B          | 145 |

| Figure A2.2.1.2        | Percentage of Dynamic Instructions Due to the Unique      |     |

|                        | Computations in each Frequency Range, Global-Level,       |     |

|                        | Normalized, Input Set B                                   | 146 |

| Figure A2.2.2.1        | Frequency Distribution of Unique Computations per         |     |

|                        | Benchmark, Local-Level, Normalized, Input Set B           | 148 |

| <b>Figure A2.2.2.2</b> | Percentage of Dynamic Instructions Due to the Unique      |     |

|                        | Computations in each Frequency Range, Local-Level,        |     |

|                        | Normalized, Input Set B                                   | 149 |

| Figure A3.2.1          | Percentage of Trivial Computations per Instruction Type   |     |

|------------------------|-----------------------------------------------------------|-----|

|                        | and per Total Number of Dynamic Instructions for the      |     |

|                        | SPEC and MediaBench Benchmarks                            | 151 |

| <b>Figure A6.1.1.1</b> | Speedup Due to Instruction Precomputation; Profile Input  |     |

|                        | Set B, Run Input Set B, Frequency                         | 152 |

| <b>Figure A6.1.2.1</b> | Speedup Due to Instruction Precomputation; Profile Input  |     |

|                        | Set A, Run Input Set B, Frequency                         | 153 |

| <b>Figure A6.1.3.1</b> | Speedup Due to Instruction Precomputation; Profile Input  |     |

|                        | Set AB, Run Input Set B, Frequency                        | 154 |

| <b>Figure A6.1.4.1</b> | Speedup Due to Instruction Precomputation for the Highest |     |

|                        | Frequency and Latency Product Unique Computations;        |     |

|                        | Profile A, Run B                                          | 155 |

| <b>Figure A6.1.4.2</b> | Speedup Due to Instruction Precomputation for the Highest |     |

|                        | Frequency and Latency Product Unique Computations;        |     |

|                        | Profile A, Run A                                          | 156 |

| <b>Figure A6.1.4.3</b> | Speedup Due to Instruction Precomputation for the Highest |     |

|                        | Frequency and Latency Product Unique Computations;        |     |

|                        | Profile B, Run B                                          | 157 |

| <b>Figure A6.1.4.4</b> | Speedup Due to Instruction Precomputation for the Highest |     |

|                        | Frequency and Latency Product Unique Computations;        |     |

|                        | Profile AB, Run A                                         | 158 |

| <b>Figure A6.1.4.5</b> | Speedup Due to Instruction Precomputation for the Highest |     |

|                        | Frequency and Latency Product Unique Computations;        |     |

|                        | Profile AB, Run B                                         | 159 |

| <b>Figure A6.1.5.1</b> | Speedup Due to Value Reuse; Run B                         | 160 |

| <b>Figure A6.2.1.1</b> | Speedup Due to the Simplification and Elimination of      |     |

|                        | Trivial Computations for Selected SPEC 2000               |     |

|                        | Benchmarks, Realistic Processor Configuration, Input Set  |     |

|                        | В                                                         | 161 |

| <b>Figure A6.2.1.2</b> | Speedup Due to the Simplification and Elimination of      |     |

|                        | Trivial Computations for Selected MediaBench              |     |

|                        | Benchmarks, Realistic Processor Configuration, Input Set |     |

|------------------------|----------------------------------------------------------|-----|

|                        | В                                                        | 162 |

| <b>Figure A6.2.2.1</b> | Speedup Due to the Simplification and Elimination of     |     |

|                        | Trivial Computations for Selected SPEC 2000              |     |

|                        | Benchmarks, Enhanced Processor Configuration, Input Set  |     |

|                        | В                                                        | 163 |

| <b>Figure A6.2.2.2</b> | Speedup Due to the Simplification and Elimination of     |     |

|                        | Trivial Computations for Selected MediaBench             |     |

|                        | Benchmarks, Enhanced Processor Configuration, Input Set  |     |

|                        | В                                                        | 164 |

# **List of Tables**

| <b>Table 2.2.1</b>   | Example Unique Computations                                | 22 |

|----------------------|------------------------------------------------------------|----|

| <b>Table 2.2.1.1</b> | Characteristics of the Unique Computations for the Top     |    |

|                      | 2048 Global-Level Unique Computations, by Frequency        | 26 |

| <b>Table 2.2.2.1</b> | Percentage of Instructions Due to the 2048 Highest         |    |

|                      | Frequency Unique Computations at the Global and Local      |    |

|                      | Levels                                                     | 29 |

| <b>Table 2.3.1</b>   | Number of Unique Computations that are Present in Two      |    |

|                      | Sets of the 2048 Highest Frequency Unique Computations     |    |

|                      | from Two Different Input Sets                              | 30 |

| <b>Table 3.2.1</b>   | List of Trivial Computations                               | 38 |

| <b>Table 3.2.2</b>   | Trivial Computations that Benefit From Non-Speculative,    |    |

|                      | Early Execution                                            | 38 |

| <b>Table 4.2.2.1</b> | Plackett and Burman Design Matrix with Foldover (X=8)      | 57 |

| <b>Table 5.2.1</b>   | Key Processor and Memory Parameters for the                |    |

|                      | Performance Evaluation of Instruction Precomputation and   |    |

|                      | the Simplification and Elimination of Trivial Computations | 68 |

| <b>Table 5.3.1</b>   | Processor Core Parameters and Their Plackett and Burman    |    |

|                      | Values                                                     | 70 |

| <b>Table 5.3.2</b>   | Functional Units Parameters and Their Plackett and         |    |

|                      | Burman Values                                              | 70 |

| <b>Table 5.3.3</b>   | Memory Hierarchy Parameters and Their Plackett and         |    |

|                      | Burman Values                                              | 71 |

| <b>Table 5.4.1</b>   | Selected SPEC CPU 2000 Benchmarks and Input Sets           |    |

|                      | (Dynamic Instruction Count in Millions of Instructions)    | 73 |

| <b>Table 5.4.2</b>   | Selected MediaBench Benchmarks and Input Sets              |    |

|                      | (Dynamic Instruction Count in Millions of Instructions)    | 74 |

| <b>Table 5.4.3</b>    | Selected SPEC CPU 2000 Benchmarks with the Large          |     |

|-----------------------|-----------------------------------------------------------|-----|

|                       | Input Set (Dynamic Instruction Count in Millions of       |     |

|                       | Instructions)                                             | 74  |

| <b>Table 6.1.2.1</b>  | Speedup Due to Instruction Precomputation for mesa;       |     |

|                       | Profile Input Set A, Run Input Set A versus Profile Input |     |

|                       | set B, Run Input Set A, Frequency                         | 81  |

| <b>Table 6.1.3.1</b>  | Number of Unique Computations that are Present in Two     |     |

|                       | Sets of 2048 of the Highest Frequency Unique              |     |

|                       | Computations from Two Different Input Sets                | 84  |

| <b>Table 6.3.1.1</b>  | Plackett and Burman Design Results for All Processor      |     |

|                       | Parameters; Ranked by Significance and Sorted by the      |     |

|                       | Average Sum-of-Ranks                                      | 97  |

| <b>Table 6.3.1.2</b>  | Plackett and Burman Design Results for All Processor      |     |

|                       | Parameters; Ranked by Significance and Sorted by the      |     |

|                       | Average Sum-of-Ranks; Reduced Cache Sizes                 | 100 |

| <b>Table 6.3.2.1</b>  | Example of Benchmark Selection, Choosing Eight            |     |

|                       | Benchmarks from Thirteen                                  | 103 |

| <b>Table 6.3.3.1</b>  | Plackett and Burman Design Results for All Processor      |     |

|                       | Parameters When Using Instruction Precomputation;         |     |

|                       | Ranked by Significance and Sorted by the Average Sum-     |     |

|                       | of-Ranks                                                  | 105 |

| <b>Table 6.3.3.1</b>  | Plackett and Burman Design Results for All Processor      |     |

|                       | Parameters When Simplifying and Eliminating Trivial       |     |

|                       | Computations; Ranked by Significance and Sorted by the    |     |

|                       | Average Sum-of-Ranks                                      | 107 |

| <b>Table A2.2.1.1</b> | Characteristics of the Unique Computations for the Top    |     |

|                       | 2048 Global-Level Unique Computations, Input Set B        | 147 |

| <b>Table A2.2.2.1</b> | Percentage of Instructions Due to the 2048 Highest        |     |

|                       | Frequency Unique Computations at the Global and Local     |     |

|                       | Levels, Input Set B                                       | 150 |

Table A4.1 Selected MediaBench Benchmarks and Input Sets

(Dynamic Instruction Count in Millions of Instructions),

Input Set B 151

### **Abstract**

Although current commercial processors are capable of fetching and executing multiple instructions per cycle, processor resources such as issue slots, functional units, and buffers are frequently idle due to the lack of available instruction-level parallelism. As a result, the processor's actual performance is often far below its theoretical maximum performance. To increase the amount of instruction-level parallelism, this dissertation proposes two microarchitectural techniques that dynamically remove redundant and trivial computations. A redundant computation is a computation that the processor performs repeatedly during the course of a program's execution while a trivial computation is one where the output is zero, one, 0xffffffff, or a shifted version of one of the inputs.

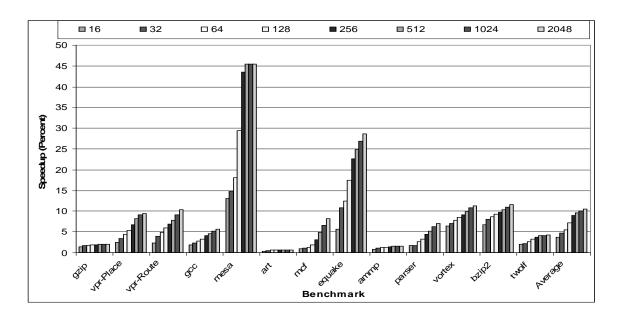

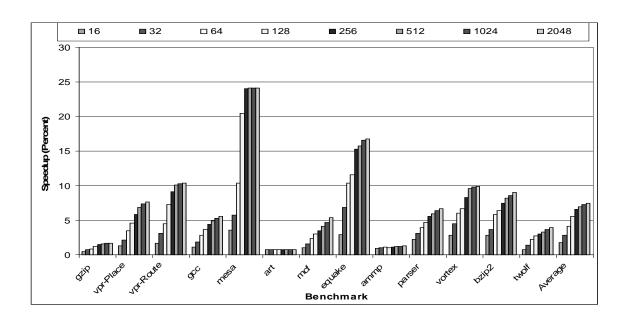

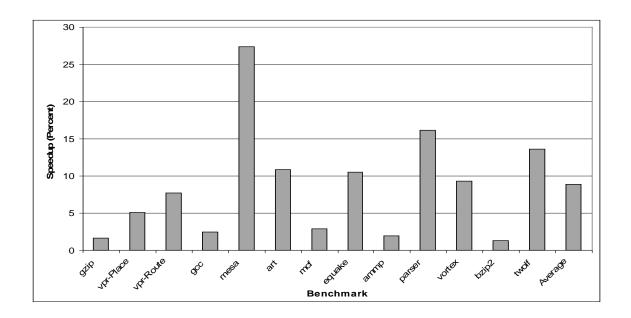

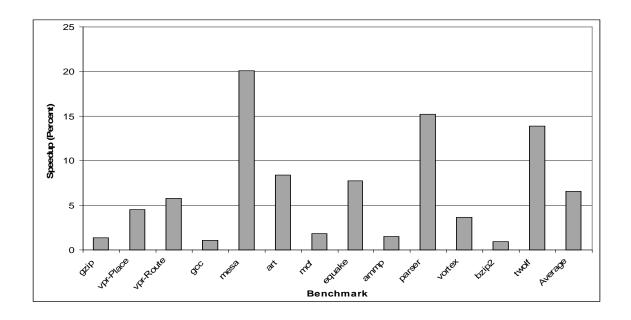

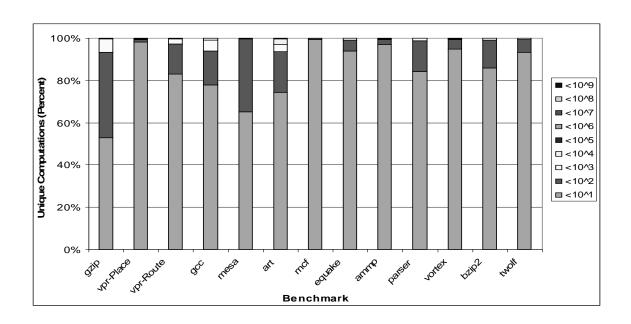

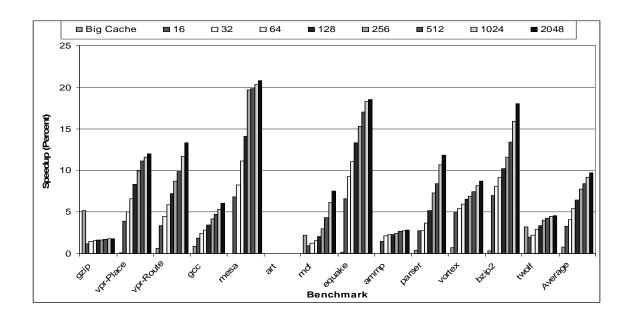

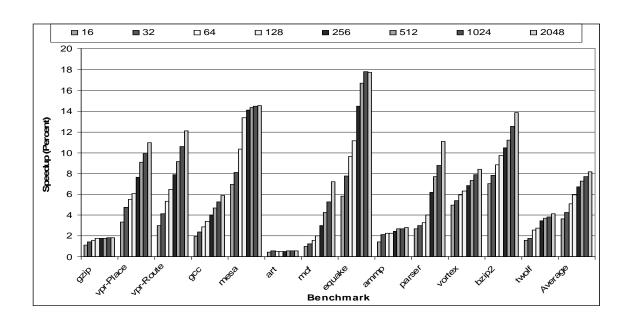

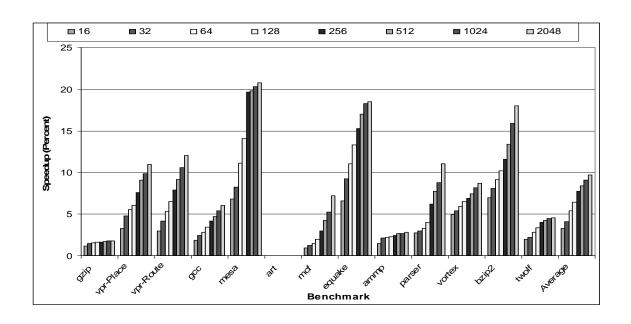

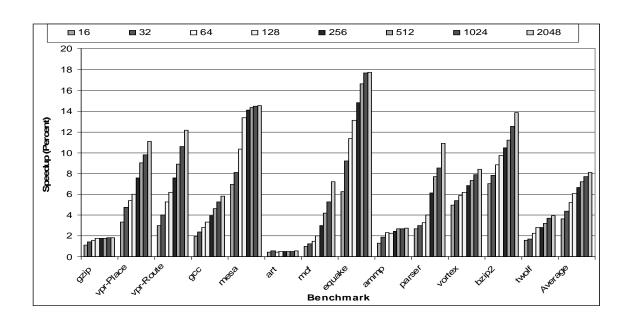

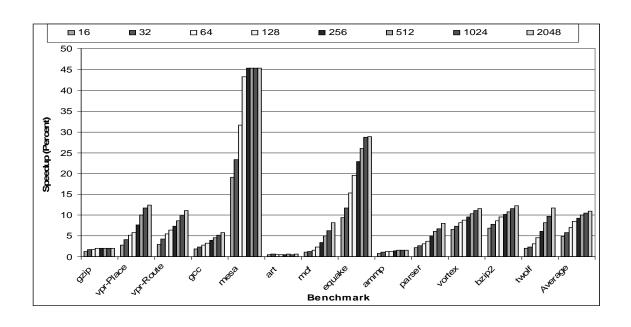

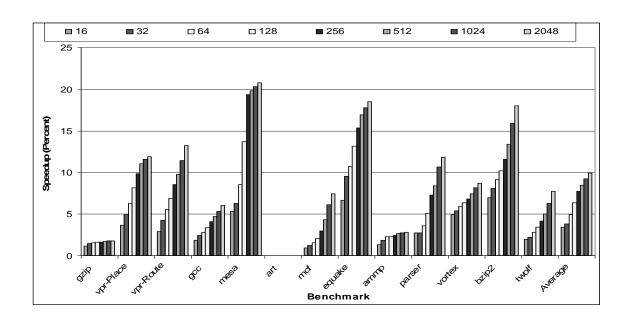

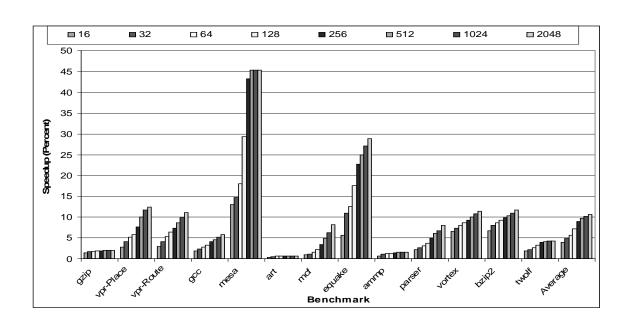

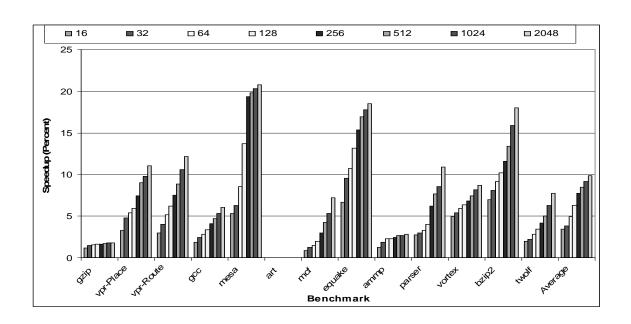

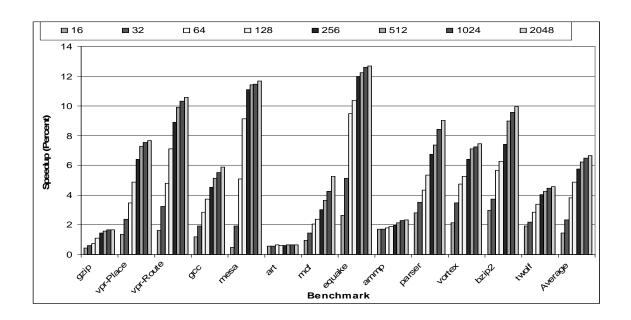

The first technique, Instruction Precomputation, compares each instruction's opcode and input operands against the opcode and input operands that are stored in the Precomputation Table. If the opcodes and input operands match, the Precomputation Table forwards the result for that redundant computation to the associated instruction. Our results show that the 2048 highest frequency redundant computations account for 14.68% to 44.49% of the total dynamic instruction count. Using Instruction Precomputation to dynamically remove these redundant computations yields speedups of

0.71% to 45.40%, with an average of 10.53%, when using a 2048-entry Precomputation Table.

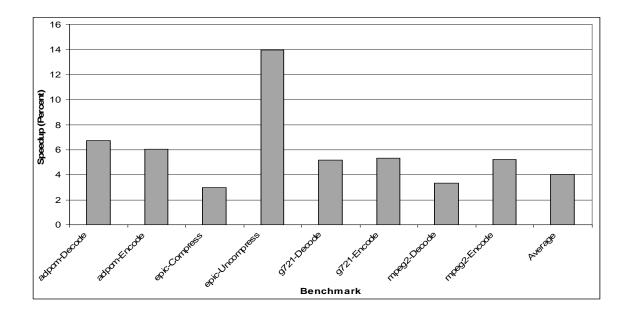

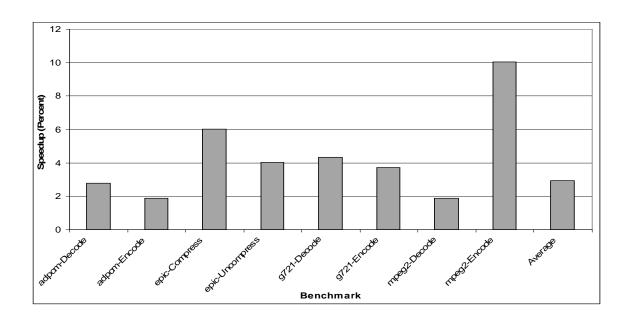

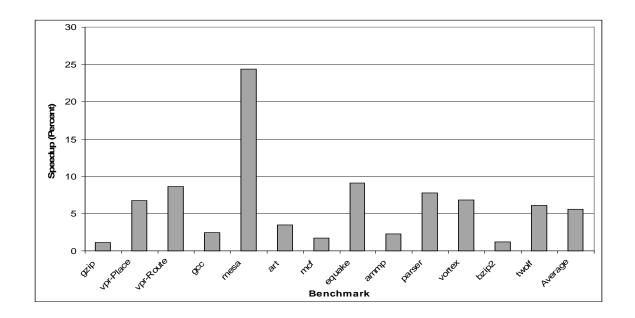

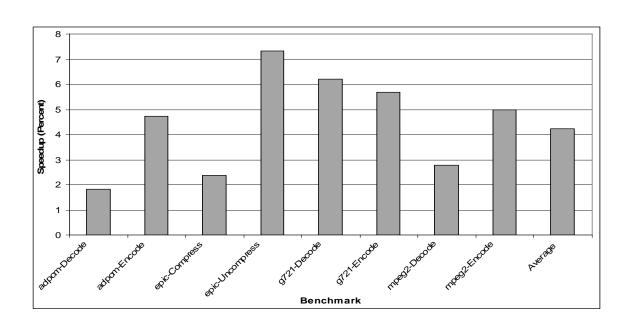

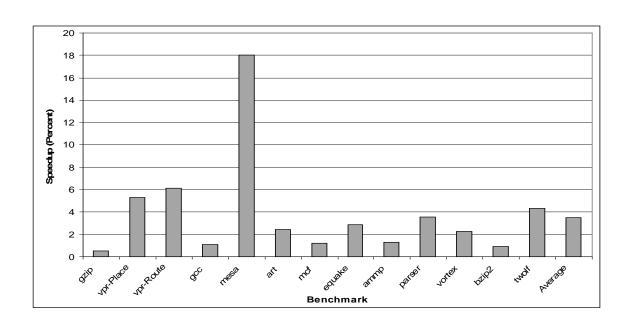

The second technique, the Simplification and Elimination of Trivial Computations, checks the opcode and input operands of each instruction to determine whether or not that computation is trivial or not. When the trivial computation can be simplified, the instruction is converted to another type of instruction that produces the same result, but with a lower execution frequency. When the trivial computation can be eliminated, the trivial computation hardware "computes" its result and removes the instruction from the pipeline. Our results show that 12.24% and 5.73% of all dynamic instructions in selected SPEC 2000 and MediaBench, respectively, benchmarks are trivial computations. Adding hardware to exploit these trivial computations yields speedups of 1.31% to 27.36%, with an average of 8.86%, for the SPEC 2000 benchmarks and speedups of 2.97% to 13.97%, with an average of 4.00%, for the MediaBench benchmarks.

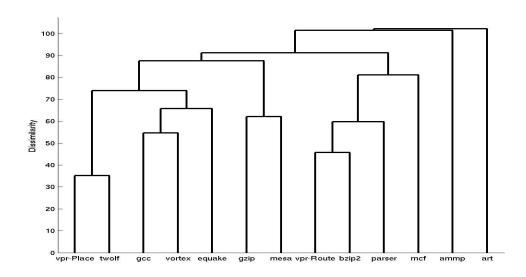

Finally, due to cost, time, and flexibility constraints, simulators are used in the design and implementation of next-generation processors and to evaluate the performance of processor enhancements. Despite this dependence on simulators, computer architects usually approach the simulation process in an ad-hoc manner. Mistakes and irregularities in the simulation process may introduce errors into the simulation results. On the other hand, using statistically-based simulation methodology helps the architect decrease the number of errors in the simulation process, gives more insight into the effect of a processor design or enhancement, and provides statistical support to the observed behavior. This dissertation proposes and demonstrates the efficacy of using the statistical Plackett and Burman design to improve how processor parameter values are chosen, how benchmarks are chosen, and how processor enhancements are analyzed. In particular, the results show the effect that Instruction Precomputation and exploiting trivial computations have on the processor.

This dissertation makes the following primary contributions. First, this dissertation quantifies the amount of redundant and trivial computations that are present in typical

programs. Second, to exploit these two program characteristics, this dissertation proposes and demonstrates the performance potential of two microarchitectural enhancements: Instruction Precomputation and Simplifying and Eliminating Trivial Computations. Finally, this dissertation identifies problems with existing simulation methodologies and offers specific, statistically-based recommendations to improve the overall quality of simulation methodology.

## **Chapter 1**

## Introduction

In the past few years, superscalar processors have become the most popular processor architecture due to their high-performance. Examples of superscalar processors include the Alpha 21264 [Kessler98, Kessler99, Leiholz97], the MIPS R10000 [Yeager96], the UltraSparc III [Horel99], and the PA-RISC 8000 [Kumar97]. To achieve even more performance, processor designers can increase the clock frequency and/or increase the number of instructions that the processor decodes, issues, executes, and retires per clock cycle.

Since higher clock frequencies do not yield proportional increases in the processor's performance and since the maximum clock frequency is constrained by the minimum transistor width, processor designers primarily try to improve the processor's performance by maximizing the number of retired instructions per cycle. While current-generation processors are capable of decoding, issuing, executing, and retiring several instructions in a single cycle, only independent instructions can be issued in the same cycle. One measure of how independent the instructions are for a given region of a program is the amount of instruction-level parallelism (ILP). The next two sections briefly discuss the key components of superscalar processors and the effect that dependences between instructions have on the ILP.

#### 1.1. Superscalar Microprocessors

As specified by the von Neumann model [Hennessy96], the two main components of modern processors are the execution core and memory. Caches, the memory structures closest to the processor (in terms of access time), are used to hold recently accessed data and instructions. To improve the performance of retrieving data and instructions, the L1 Caches – the caches closest to the processor – are split into separate caches, one for data and one for instructions. This model of cache partitioning is called the Harvard Architecture [Hennessy96].

The L1 Instruction Cache (or I-Cache), the L1 Data Cache (D-Cache), and the L2 Cache buffer instructions and data that will likely be needed in the near future. When using these caches, instead of retrieving the requested blocks from main memory – which requires hundreds of cycles – the requested blocks can be retrieved from a cache. Consequently, reducing the access time for those memory blocks reduces the overall program execution time.

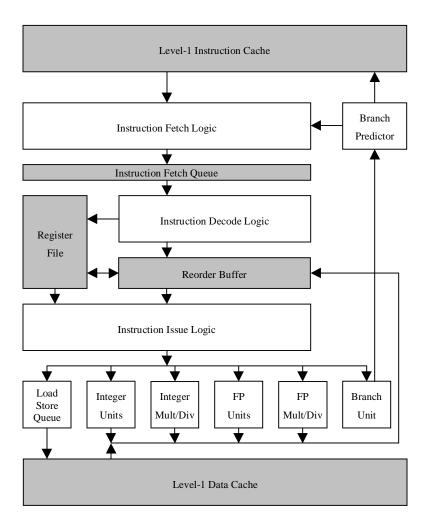

The purpose of the execution core is to execute the assembly-level instructions of the program. Its main components are: the instruction fetch logic, the branch predictor and target buffer, the decode logic, the register file, the reorder buffer (ROB), the issue logic, and the functional units. The instruction fetch logic uses predictions and target addresses from the branch predictor and target buffer, respectively, to efficiently retrieve instructions from memory and store them into the instruction fetch queue (IFQ). The decode logic decodes instructions in the IFQ, retrieves their input operands from the register file or ROB, and moves the decoded instructions into the ROB. In addition to buffering the current state of each in-flight instruction, the ROB stores and also retires these instructions in program order to support precise exceptions. The issue logic determines which instructions are ready to execute – the ones that have all of their input operand values – and sends them to the functional units. The functional units compute

the results of arithmetic and logical instructions, store or load data values to and from the memory hierarchy, and determine the branch direction and target.

Figure 1.1.1 shows the functional-level organization of the typical superscalar processor. To improve the readability of the figure, the branch target buffer is represented by the branch predictor. For the same reason, the L2 Cache and main memory are omitted.

Figure 1.1.1: Functional-Level Organization of a Superscalar Processor

The hallmark of superscalar processors is that they fetch, decode, execute, and retire multiple instructions per cycle. Consequently, the fetch logic, the decode logic, and the functional units operate on several instructions every cycle.

However, due to branch instructions – or control dependences, the average number of fetched instructions is often far below the fetch width (maximum number of instructions that can be fetched per cycle). By lowering the average number of instructions that are fetched per cycle, control dependences also reduce the number of instructions that are being decoded, executed, or retired in any given cycle. Branch predictors, branch target buffers, and instruction fetch queues minimize, but cannot completely eliminate, the effect of control dependences.

#### 1.2. Instruction-Level Parallelism and Data Dependences

In addition to control dependences, data dependences also reduce the actual performance from the theoretical peak performance. A read-after-write (RAW) data dependence exists between two instructions if the result of the first instruction is used to calculate the result of the second. For example, consider the assembly code shown in Figure 1.2.1.

```

loop:

lw

r1,r2

; r1 = Mem[r2]

add

r1,r2,r3

; r1 = r2 + r3

sub

r4,r1,r5

; r4 = r1 - r5

r1,r2,r3

; r1 = r2 * r3

mul

sra

r2,r1,1

; r2 = r1 >> 1

r7,r1,loop

; Branch if r7 = r1

beq

```

Figure 1.2.1: Assembly Code Example of Read-After-Write Dependences

In Figure 1.2.1, RAW data dependences exist between the add and sub instructions as well as between the mul and sra instructions. In the former pair, the add computes and then stores a value into register r1, which the sub instruction uses as an input value. In the latter pair, the mul instruction stores its result in register r1, which is subsequently read by the following instruction (sra). For each pair of the instructions, the second instruction cannot execute before the first since it needs the result of the first.

Consequently, a RAW data dependence exists between the first and second instructions of each pair through register r1.

Figure 1.2.1 also shows two other types of data dependences: write-after-write (WAW) and write-after-read (WAR). A WAW data dependence occurs when two instructions write to the same register value. For example, in Figure 1.2.1, WAW data dependences exist between the 1w and add instructions as well as between the add and mul instructions, both through register r1. For each pair of instructions, the second instruction cannot write its output value to the shared register until after the first instruction has written its output value.

The WAR data dependence exists between two instructions if the second instruction writes to a register that the first reads from. In Figure 1.2.1, WAR dependences exist between the sub and mul instructions through register r1 as well as between the mul and the sra instructions through register r2. Due to this dependence, the second instruction cannot write its output value to the shared register until after the first has read the register.

Since data dependences exist between instructions, the processor cannot issue or execute those instructions completely in parallel. This has two important ramifications. First of all, since processors are designed with enough resources to issue and execute multiple instructions in parallel, processor resources are idle when executing instructions with data dependences. Second, the serial execution of these instructions reduces the processor's performance from its theoretical maximum. Therefore, to improve the processor's resource utilization efficiency and, more importantly, to improve its actual overall performance, it is imperative to decrease the number of dependent instructions.

In addition to control and data dependences, the other major factor that limits the amount of ILP is the execution latency of instructions, or more specifically, the execution latency of load instructions. While many instructions have multi-cycle execution latencies, load instructions latencies have a disproportionately large effect on the performance since they

have a very wide range of latencies, despite using multi-level data caches and other microarchitectural techniques such as out-of-order execution and prefetching. Instructions with very long execution latencies limit the amount of ILP by reducing the rate at which instructions are executed by the processor.

In summary, the number of instructions that can be issued and executed in parallel is primarily limited by the amount of ILP. Control and data dependences, in addition to long and variable instruction latencies, have a very large, negative effect on the processor's performance. Therefore, to improve the processor's performance, computer architects try to break the control and data dependences or reduce the effective instruction latency. The next few sub-sections introduce two techniques — **Instruction Precomputation** and the **Simplification and Elimination of Trivial Computations** — that attempt to break data dependences and reduce the execution latency.

#### 1.3. Superscalar Performance

There are many different ways to measure a processor's performance, such as speedup, SPEC number, millions of instructions per second (MIPS), etc. [Lilja00], but one of the more meaningful metrics – and perhaps the most important – is the total execution time of the program on that particular processor. The total amount of time it takes to execute a program is approximated by Equation 1.3.1.

$$T_e = n * CPI * T_c$$

#### **Equation 1.3.1: Formula for the Total Program Execution Time**

Where

n Total number of executed instructions

CPI Average number of cycles needed to execute an instruction

T<sub>c</sub> Time per clock period (cycle)

Note that the reciprocal of CPI (cycles per instruction) is IPC (instructions per cycle).

Equation 1.3.1 shows that the execution time  $T_e$  is proportional to n, CPI, and  $T_c$ . Consequently, to reduce the program's total execution time, it is necessary to either: 1) Reduce the number of executed instructions, 2) Decrease the average execution time of each instruction, and/or 3) Decrease the clock period. However, since the number of instructions in the program cannot be reduced at run-time (i.e. by hardware) and since clock period is based on the minimum transistor width, the only viable option for computer architects to reduce the program's execution time is to reduce the CPI.

#### **1.4.** Redundant Computations

During the course of a program's execution, a processor executes many redundant computations. A redundant computation is a computation that the processor had performed earlier in the program. For example, consider the code fragment shown in Figure 1.4.1:

```

for (i=0; i < MAX; i++)

{

for (j=0; j < MAX; j++)

{

...

}</pre>

```

Figure 1.4.1: Example of a Source of Redundant Computations

For each iteration of the outer loop, the calculations for the loop index variable j are exactly the same. More specifically, the calculations for j are: 0+1, 1+1, 2+1, ..., 98+1, 99+1, 0+1, 1+1, 2+1, ..., 98+1, 99+1, 0+1, etc. Therefore, after the first iteration of the outer loop, all the computations to compute each value of j are redundant.

It is important to note that redundant computations are not limited only to add instructions. Rather, any and all computations can be redundant. Furthermore, it is also important to note that an optimizing compiler may not be able to remove these redundant computations during the compilation process since the actual input operand values may be unknown at compile time – possibly because they depend on the inputs to the program.

Redundant computations can be divided into global and local level redundant computations. The difference between the two is that the global-level redundant computations are independent of the Program Counter (PC) while local-level redundant computations are dependent on the PC. Figure 1.4.2 illustrates the difference between the two levels.

```

add r1,r1,#1 ; r1 = r1 + 1

; 0+1, 1+1, 2+1, 3+1, 4+1, ..., 98+1, 99+1

...

add r2,r3,r4 ; r2 = r3 + r4

; 1+0, 1+1, 1+2, 1+3, 1+4, ..., 1+98, 1+99

```

Figure 1.4.2: Example of Global and Local Level Redundant Computations

In this example, there are no local-level redundant computations since either instruction does not, itself, repeat a computation. However, at the global-level, there are 100 redundant computations since both instructions perform the same operations on the same input operand values. From this example, it is obviously that there are more redundant computations at the global-level, which is an important distinction when trying to improve the processor's performance by exploiting redundant computations.

Redundant computations affect the program's execution time in two ways. First of all, executing the instructions for redundant computations increases the program's dynamic instruction count. Secondly, these redundant computations affect the average CPI since

they produce values for other instructions in the program. However, these redundant computations need to be executed to ensure correct program operation. Additionally, all of the instances of these instructions may not be redundant computations. Consequently, the hardware cannot simply disregard these computations at run-time to decrease the program's execution time. Thus, the only recourse to improve the processor's performance, with respect to redundant computations, is to reduce the CPI of the redundant computations.

#### 1.5. Value Reuse: Effect and Shortcomings

Value reuse [Sodani97, Sodani98] is a microarchitectural technique that improves the processor's performance by dynamically removing redundant computations from the processor's pipeline. During the program's execution, the value reuse hardware compares the opcode and input operand values of the current instruction against the opcodes and input operand values (hereafter, alternatively referred to as a **unique computation**) of all recently executed instructions, which are stored in the value reuse table (VRT). If there is match between the opcodes and input operand values, then the current instruction is a redundant computation and, instead of continuing its execution, the current instruction gets its output value from the result stored in the VRT. On the other hand, if the current instruction's opcode and input operand values do not match those found in the value reuse table, then the instruction is not a recent redundant computation and it executes normally. After finishing execution, the value reuse hardware stores the opcode, input operand values, and output value for that instruction into the VRT.

While value reuse increases the amount of ILP – thus improving the processor's performance – it does not necessarily effectively target the redundant computations that have the most effect on the program's execution time. This shortcoming stems from the fact that the VRT is finite in size. Consequently, when all entries of the VRT are occupied and when the current instruction tries to store its unique computation and output

value into the VRT, the contents of one entry are overwritten. However, if the current unique computation is executed less often than that of the one it replaces, then the current unique computation is less useful in increasing the amount of ILP since it occurs less often. In other words, due to dynamic replacement, the entries in the VRT are not necessarily the unique computations that have the greatest impact on the total program execution time.

To address this problem, this dissertation proposes a microarchitectural technique called **Instruction Precomputation**.

#### 1.6. Instruction Precomputation

As described in the previous sub-section, one problem with value reuse is that a unique computation with a low frequency of execution could replace a high frequency one. However, since it is virtually impossible for hardware to determine at run-time which unique computations have the highest frequencies of execution, Instruction Precomputation uses feedback-directed optimization to first determine, at compile-time, the highest frequency unique computations. At run-time, those unique computations are then loaded into the Precomputation Table (PT), which is very similar to the VRT with the key exception that entries in the PT are not updated during the program's execution. In other words, in value reuse, the hardware determines which unique computations should be in the VRT while in Instruction Precomputation, the compiler controls which unique computations are in the PT.

Using the compiler to statically determine which unique computations have the highest frequencies has two key advantages over using hardware. First, and most importantly, the compiler is able to determine if a unique computation is a high frequency unique computation or not. Although the compiler only profiles the program with one or two different inputs, previous work showed that the same program with different inputs sets had many high frequency unique computations in common. In other words, determining

the highest frequency unique computations of a program with a specific input will most likely yield the highest frequency unique computations for the same program, but with a different input. Second, determining the highest frequency unique computations with the compiler means that fewer access ports are needed to access the PT. When the hardware is used to profile a program, additional access ports are needed to allow the hardware to write to the table. However, when using the compiler, the PT is never updated. Therefore, no additional write ports are needed. Having fewer access ports results in a lower PT access time, which means that Instruction Precomputation has a lower impact on the clock period.

#### 1.7. Simplification and Elimination of Trivial Computations

In addition to repeatedly performing many redundant computations during the course of the program's execution, the processor also executes many trivial computations. A trivial computation can be defined as a computation where the output value is zero, one, or a shifted version of one of the input operands. For example, using definitions given in this dissertation, each of the following computations are trivial: X+0, X-X, X\*2, and X/1. Since these particular computations are trivial – or more precisely, their output value is trivial – the processor can reduce the execution latency of these computations either by "calculating" the output value without using a functional unit or by simplifying the computation so it can use a functional unit with a lower execution latency. The remainder of this sub-section describes in more detail how trivial computations can be simplified or eliminated to improve the processor's performance.

As in the case of redundant computations, it is important to note that an optimizing compiler may not be able to remove these trivial computations since the actual input operand values may be unknown at compile time. As a result, removing or optimizing the execution of these trivial computations is best left to the hardware.

Trivial computations affect the program's execution time in the same two ways as do redundant computations. First of all, performing trivial computations increases the program's dynamic instruction count. Second, performing these trivial computations increases the overall, average CPI since these instructions produce input values for other instructions in the program. However, since these trivial computations need to be performed for correct program execution, to minimize their effect on the processor's performance, the only recourse is to reduce their latency.

As described in the previous sub-section, there are two methods to reduce the CPI of trivial computations. In the first method, the processor eliminates the trivial computation completely by computing the final result of the instruction without a functional unit. In the second method, the processor reduces the complexity, and consequently the execution latency, of the trivial computation by converting the operation into another operation.

For example, consider the following computations: X-X and X\*4, where X is the value of one the input operands. Since the result of the first computation will be zero, regardless of the value of X, it is pointless to perform that computation using a functional unit since the result is trivial. In this particular case, by assigning the value of zero to that computation, the trivial computation hardware can reduce the execution latency of this instruction.

The result of the second computation is simply the value of X shifted to the left by two bit positions. Therefore, instead of performing this computation normally by using an integer multiply unit, the processor can perform this computation by converting this computation to a shift-left operation. And since shifts have a lower latency as compared to multiplies, dynamically changing the instruction from a multiply instruction to a shift-left instruction will decrease the CPI for this instruction, thus decreasing the overall program execution time.

In addition to reducing the execution latency of trivial computations, eliminating these trivial computations also has another key benefit: non-speculative early instruction execution. For most superscalar processors, an instruction is issued (sent to the functional units) only after it has been decoded and after it has received the values for both its input operands. However, for the trivial computations that can be eliminated, if `the instruction has received the value for the trivial input (e.g. 0 for X\*0), the instruction does not need to wait for the other input operand value to arrive since the output can be computed purely as a result of the trivial one. Consequently, by exploiting these trivial computations in this way, the processor can exceed the dataflow limit (the maximum amount of ILP when given an infinite amount of hardware) non-speculatively.

The key difference between non-speculative and speculative instruction execution is that the output value of the latter is computed based on predicting what its input values might be, executing it with those input values (generating a speculative output value), and then executing any dependent instructions with that speculative output value. Therefore, before that instruction can be committed, the processor needs to verify if the input values were correctly predicted. If so, the output value of that instruction and any dependent instructions can be written to the register file. If not, then the processor needs to reexecute all dependent instructions that used the incorrect value. For those instructions that can be executed non-speculatively, the processor does not need to check if the prediction is correct (since no prediction was made) and can immediately commit its output value.

#### 1.8. The Efficacy, Utility, and Necessity of Simulators

Simulators are the most important tool in computer architecture research. Due to cost, time, and flexibility constraints, simulators are often used to explore the design space when developing a new processor architecture or to evaluate the effectiveness of a proposed processor enhancement (hardware or software). For instance, simulators reduce the cost and development time of a new processor design by giving the architecture design team ballpark estimates of the processor's performance. Without simulators in this case, the team would have to use intuition or actually fabricate the chip to evaluate

the performance of each candidate design. Consequently, without simulators, designing processors either would be too expensive or would yield very poor designs.

#### 1.9. Deficiencies of Existing Simulation Methodologies

Despite this level of dependence on simulators, computer architects usually approach the simulation process in an ad-hoc manner. Consequently, the results that computer architects obtain from their simulations may be not completely accurate, or worse yet, may be misleading. Furthermore, an ad-hoc simulation methodology does not necessarily extract the maximum amount of information from the results.

For example, a sensitivity analysis is frequently utilized to determine the effect that different processor parameters have on a processor enhancement. To test the effect of each parameter, the computer architect will vary one or more parameters at a time while holding the other parameters at a constant value and measure the effect of the variable parameter(s) on the processor enhancement. However, before starting the simulations, several questions about sensitivity analysis itself need to be answered. For example, which parameters should be varied? What range of values should be used for those parameters? Do any of the constant parameters interact with the variable ones? What is the magnitude of those interactions? How much impact do the specific values of the constant parameters have?

Furthermore, in addition to the questions about the sensitivity analysis setup, other questions regarding the simulation setup need to be answered. For example, which benchmarks (i.e. programs) should be used in the sensitivity analysis? Which input set (to the benchmark) should be used? If the input set is relatively short, what effects does its length have as compared to a longer input set? How should those effects be mitigated?

These questions and more are the type of questions that need to be answered before starting the simulations. However, due to the sheer computational cost, it is virtually impossible to simulate all possible combinations of parameters or to fully answer all of the simulation setup questions. This situation illustrates the need for a statistically-based simulation methodology.

While the downside of using such a methodology is that it may require some additional simulations, it also has the following advantages:

- 1) It decreases the number of errors that are present in the simulation process and helps the computer architect detect errors more quickly. Errors include, but are not limited to, simulator modeling errors, user implementation errors, and simulation setup errors [Black98, Cain02, Desikan01, Gibson00, Glamm00].

- 2) It gives more insight into what is occurring inside the processor or the actual effect that a processor enhancement has on the processor.

- 3) It gives objective confidence to the results and provides statistical support regarding the observed behavior.

While the first and third advantages are self-explanatory, it is not obvious from the second advantage how a statistically-based methodology could improve the quality of the analysis. Since simulators are complex, it is very difficult to fully understand the effect that a design change or an enhancement may have on the processor. As a result, architects use high-level single-value metrics, such as speedup or cache miss rate, to understand the "big-picture" effects. Unfortunately for this approach, these high-level metrics sacrifice information for conciseness by discarding most of the information that is available to the simulator for a single, neat assessment of the performance. Consequently, important conclusions that are more subtle are overlooked. Furthermore, since much information is discarded, only the net effect on the final metric of two competing effects is known.

For example, suppose a new prefetching mechanism improves the processor's performance by 20%. Also suppose that in this case that this prefetching mechanism decreases the importance of the cache's associativity, but dramatically magnifies any shortage in the number of load-store queue (LSQ) entries. While this may be the case, the speedup only shows the net result of the associativity's decreased effect and the increased effect of the LSQ entries. As a result, while the overall speedup is quite good, further analysis would reveal that this prefetching mechanism also moves the performance bottleneck from the cache associativity to the LSQ entries.

Therefore, basing conclusions on a single high-level metric can be dangerous since that metric shows the "big picture" only at a distance. However, analyzing the processor from a statistical point-of-view can help the architect quantify the effects that all components have on the performance and on other important design metrics (e.g. power consumption, etc.).

More specifically, this dissertation improves the simulation methodology used by computer architects by recommending specific procedures on how to:

- 1) Choose the processor parameter values.

- 2) Select a sub-set of benchmarks.

- 3) Analyze the effect that an enhancement has on the processor.

The first two recommendations target the simulation setup phase of the simulation process while the last recommendation targets the analysis phase.

To illustrate the efficacy and utility of using a statistically-rigorous simulation methodology, this dissertation uses this simulation methodology when evaluating the performance of Instruction Precomputation and the Simplification and Elimination of Trivial Computations, which is described in Section 6.3.3.

#### 1.10. Contributions of this Dissertation

This Ph.D. dissertation makes the following contributions:

- 1) This dissertation quantifies the amount of redundant computations at the global-level (PC-independent) and at the local-level (PC-dependent).

- 2) This dissertation proposes a feedback-directed optimization and hardware-based processor enhancement called Instruction Precomputation that yields speedups of 4.47% and 10.52% for a small and a large PT, respectively.

- 3) This dissertation defines the range of and quantifies the amount of trivial computations.

- 4) This dissertation proposes a set of hardware mechanisms that improve the processor's performance by Simplifying and Eliminating Trivial Computations and by using a novel non-speculative scheduling mechanism. This solution improves the processor's performance by 8.22% for a typical processor and by 6.5% for an aggressive processor.

- 5) This dissertation makes specific recommendations on how to improve the simulation methodology used by computer architects. Collectively, these recommendations can improve the overall quality of the simulation methodology, decrease the total number of simulations, quickly determine the processor's bottlenecks, and provide analytical insights into the impact of processor enhancements, as compared to when no rigorous simulation methodology is used.

## 1.11. Dissertation Organization

The remainder of dissertation is organized as follows: Chapters 2 and 3 describe Instruction Precomputation and the Simplification and Elimination of Trivial Computations in more detail while Chapter 4 does the same for statistically-based simulation methodology. Chapter 5 describes the simulator, benchmarks, and input sets that were used while Chapter 6 describes performance results for Instruction Precomputation and by exploiting trivial computations. In addition, Chapter 6 also illustrates how statistically-rigorous simulation methodology can improve the simulation quality and analysis. Chapter 7 discusses previous work related to Instruction Precomputation, exploiting trivial computations, and simulation methodology. Finally, Chapter 8 describes the future work and Chapter 9 concludes.

# **Chapter 2**

# **Instruction Precomputation**

As described in Chapter 1, Instruction Precomputation is a microarchitectural technique that improves the processor's performance. The remainder of this chapter describes the problem that Instruction Precomputation attempts to solve, the program characteristic that it exploits, how it operates, and what hardware and compiler additions it needs.

# 2.1. Problems with Existing Value Reuse Mechanisms

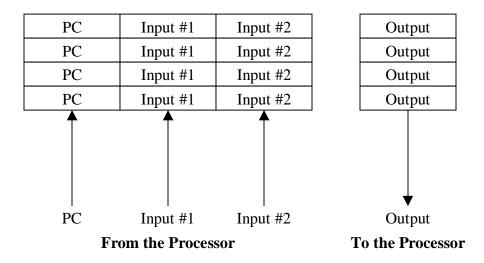

As described in Chapter 1, and in more depth in Chapter 7, value reuse [Sodani97, Molina99] is a hardware-based technique that dynamically removes instructions that are redundant computations by forwarding the results of those computations from the value reuse table (VRT) to that instruction. The VRT is an on-chip table that caches the input operands and the results of previously executed computations. The processor uses the program counter (PC) value for each instruction to access the VRT. An example of a four-entry VRT is shown in Figure 2.1.1. To access the VRT, the processor uses the instruction's PC and input operands (labeled Input #1 and Input #2) to the VRT. If the PCs and input operands match, the VRT sends the output value at that entry back to the processor and that instruction is removed from the pipeline.

Figure 2.1.1: Four-Entry Value Reuse Table and its Processor Interface

Value reuse improves the processor's performance by decreasing the execution latency of each reused instruction and by decreasing the number of resource conflicts in the issue and execute stages of the pipeline. Decreasing the latency of a reused instruction either directly or indirectly reduces the execution time of the critical path; directly if the reused instruction is on the critical path or indirectly if the reused instruction produces the value of an input operand for an instruction that is on the critical path. Furthermore, since the reused instruction does not pass through the remaining pipeline stages, the number of resource conflicts (available issue slots, functional units, reservation station entries, etc.) decreases.

While value reuse can improve the processor's performance, two problems limit its effectiveness. First of all, since the PC is used to index the VRT, value reuse can only reuse the computations associated with each static instruction. Consequently, previous computations can only be reused if that computation has already been performed for the instruction associated with that particular PC. As a result, while another instruction of that type, but with a different PC, may have previously performed that redundant computation, the result of that computation cannot be reused since the results of the second instruction cannot be accessed by the first instruction. In other words, value reuse can be exploited only if that static instruction had previously performed that computation, even though another instruction may have performed the identical computation.

Second, since the VRT is dynamically updated during the course of the program's execution, low frequency redundant computations could eventually fill a significant percentage of the VRT's entries. Replacing a high frequency redundant computation with a low frequency one reduces the number of instructions that can reuse that computation.

Overall, the net effect of these two problems is that value reuse can be rather inefficient by not reusing previously executed computations and then evicting high frequency computations in favor of lower ones. To address these two problems, and thus improve the performance of value reuse, Instruction Precomputation uses the compiler to determine the highest frequency, PC-independent redundant computations and then does not allow those high frequency redundant computations to be replaced at run-time.

## 2.2. The Amount of Redundant Computations